产品信息

半导体埋层硅外延为在已刻有电路(buried layer,埋层电路)的半导体硅抛光片上生长一层导电类型、电阻率、厚度和晶格结构都符合要求的硅单晶薄膜。相对于常规的半导体硅外延片工艺,埋层外延工艺对于外延层的电性参数分布、缺陷控制等都有更精细的要求。

|

产品参数 直径: 200 mm 外延掺值: P型-硼;N型-磷 外延层厚度: 1-50 um 外延层电阻率: 0.03-1000 ohm-cm 外延层数: 单层或多层 |

工艺介绍

半导体埋层硅外延的工艺特别需要考虑到埋层电路图形的保护,尽量减少外延生长对埋层电路图形所造成的畸变与漂移对后道光刻工艺的影响。

依托深厚的常规的半导体硅外延技术积累,我们为客户量身定制研发并代工生产的埋层半导体硅外延片产品核心技术工艺水平已比肩国际一流半导体厂商。上海合晶的技术研发部门通过特殊工艺管控外延炉的温场均匀性,解决了晶片表面图形漂移、自掺杂等埋层硅外延的各类问题,开发出优质的埋层外延产品,助力国内该项技术的发展。

由于埋层外延工艺要融入客户芯片制造的完整工艺流程,因此客户对埋层外延工艺的质量控制、生产环境、系统管控等要求与其自身一致。我们为国际一线芯片制造厂商批量代工埋层外延多年,工艺水平已达到与国际一线半导体芯片制造商水平,受到客户高度认可,是国内主要的埋层外延产品供货商之一。

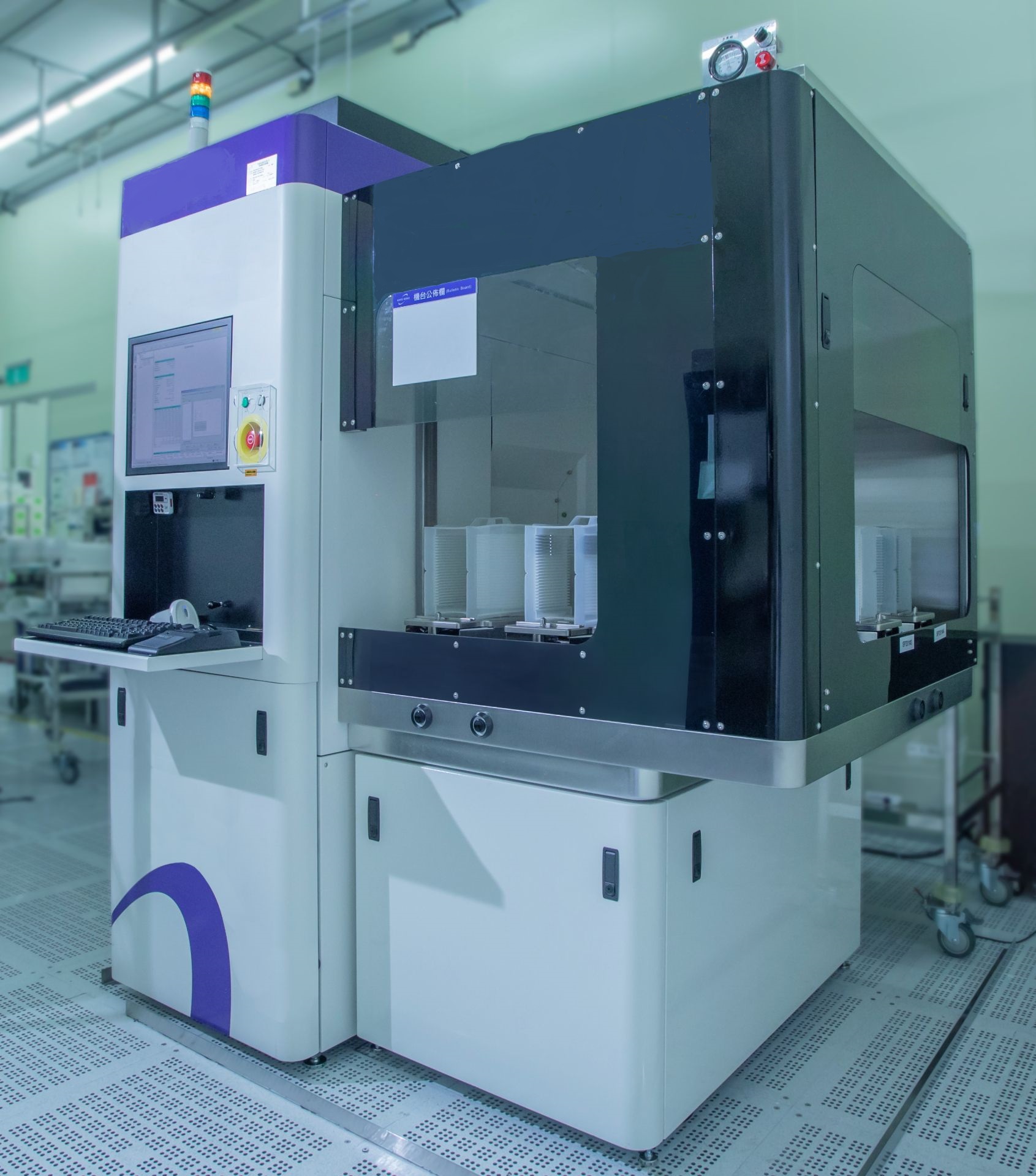

制程工序包含外延生长、外延片清洗、外延片检测及包装等。

|

外延生长 利用化学气相沉积的方式在抛光片上生长一层或多层指定厚度的单晶层,透过掺入P型硼或N型磷的混和气体来控制电阻率,并利用反应温度、外延气体的流速、中心及边缘的温度梯度的工艺调整,来调节電阻率、厚度均勻度、过渡区宽度、颗粒、缺陷(层错、滑移线、雾等)等关键参数的有效控制,保障了外延层质量,满足客户制造工艺的要求。 |

|

外延片清洗 去除硅片表面的各种污染物,例如:表面微尘颗粒、有机物、金属等各种可能的污染。 |

|

外延片检测 外延片以设备量测其电阻率、厚度、平坦度、翘曲度等物理特性值后进行最终清洗,再以高精密度的设备检测其表面微尘颗粒、有机物、金属等缺陷项目,确保外延层质量符合客户需求。 |

|

包装 以硅片盒盛装硅片后,经由包装制程于硅片盒外包覆PE袋及铝箔袋,使其在保存及运送途中,不会被环境、外力等因素破坏质量。 |

产品应用

埋层外延可以有效地减小串联电阻、简化隔离技术、提高器件性能,因此被广泛应用于电源管理(power management IC, PMIC)芯片制造等特殊工艺平台。